|

|

|

|

|

|

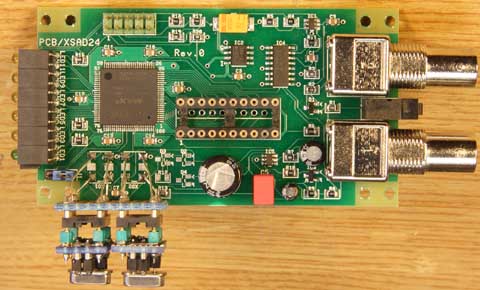

The word clock synchronization module XS-AD24, in conjunction with the AD24QS, features:

The power consumption of the ADC together with the XS-AD24 rises to 330 mA approx..

I did not make jitter measurements yet. This will become another complex task.

The XS-AD24 module is connected to the AD24QS by a 20 pin ribbon cable plugged into an IC socket that replaces the ADC's GAL. Also, the ADC's oscillator is not populated.

The size and shape of the PCB is designed so that it fits exactly

The frequency of any incoming word clock signal is compared by a CPLD whether it falls within one of the 10 bands that can be pulled-in by the VCXOs.

The algorithm that detects whether an incoming word clock signal falls within one of the 10 synchronizable bands is very fast. In the worst case (16 kHz sample rate) it needs 32 ms only and higher sample rates are detected proportionally faster.

The

Prototype

The

PrototypeThe XS-AD24 is in its prototype stage only, but this prototype, its circuit diagram and PCB-layout have turned out to be almost perfect so that the final version will require little changes only.

The final VCXOs did not arrive yet. I expect them by the end of march. That's why I tested the prototype provisionally with two self-made VCXOs, based on the oscillator-IC SN74LVC1GX04, two varicap-diodes and so on.

The PCB for the AD24QS up to

Rev.2 does not provide all signals that are necessary to supply

the XS-AD24 via the GAL's socket. Two (or better three) signals,

MClk, SClk and LRClk must be hand wired to the unused pins 6,

7 and 8 of the GAL. These pins are currently connected to VCC

and must be disconnected. Should your GAL already be socketed

and you are happy that you don't need to unsolder the GAL: Sorry,

you must unsolder the socket because one little track on the component

side underneath the socket must be cut, too :-(

The PCB for the AD24QS up to

Rev.2 does not provide all signals that are necessary to supply

the XS-AD24 via the GAL's socket. Two (or better three) signals,

MClk, SClk and LRClk must be hand wired to the unused pins 6,

7 and 8 of the GAL. These pins are currently connected to VCC

and must be disconnected. Should your GAL already be socketed

and you are happy that you don't need to unsolder the GAL: Sorry,

you must unsolder the socket because one little track on the component

side underneath the socket must be cut, too :-(

Future revisions of the ADC's PCB will be prepared for this extension.

Also, the ADC's oscillator must be disabled, e.g. by unsoldering the MK2703 or at least by disconneting its output (pin 5) from the MClk signal.

The jitter measurements I made resulted in the following table which shows the worst-case jitter performance of a word clock synchronized AD24QS system, i.e., both oscillators are running and the word clock generator's unknown jitter is included:

|

Jitter Frequency Hz |

Scale Reading dB |

Actual Jitter Value dBc/Sqrt(Hz) |

| 0.1 | -110 | -90 |

|

|

|

|

| 10 | -154 | -134 |

| 100 | not measurable | not measurable |

Click here to read the complete article about these jitter measurements.

Usually I design DIY-projects as far as possible in THT (through-hole technique). This one is almost a pure SMT (surface-mount technique) project, because the CPLD, an Altera EPM3128, and other single-gate ICs are available as SMDs (surface-mount devices) only. The idea to make DIY easy by using THDs is so much spoiled by these SMDs that it would make little sense only to design the rest in THT.

Soldering the fine-pitch ICs is easy only when you a) have enough experience and b) when you have the appropriate equipment. Otherwise it may become a catastrophe. Also, I'd like to offer this module as a kit, too, but to compile kits with small SMDs (resistors etc.) is more or less a horror. Spare parts must be supplied: One of the resistors flipped out of my tweezer, I had no spare part and I searched for it for half an hour until I gave up.

Should I offer these devices I don't know yet how to do it. Possibly pre-assembled with all SMDs by me or by a company, or possibly even completely assembled.

I was often asked for word clock synchronization for the AD24QS but I had no solution. Not only that I had no hardware to offer - I didn't even have an idea how to fulfill my technical requirements for such an additional function. The voltage controlled R/C-oscillators (VCOs) that I used to see in commercial devices were not worth to be seriously considered as their jitter values are so high that any claims on the ADC's quality ought to be thrown overboard. Thus, the word clock synchronization should be based on voltage controlled crystal-oscillators (VCXOs) in order to maintain the ADC's original jitter quality when it is externally synchronized.

One problem is to find suitable VCXOs. They cannot be bought from stock, particularly not for reasonable prices(!). While 24.576 MHz is not an unusual frequency and a slight chance might exist to find one, I am convinced that there will be no chance for 22.5792 MHz. I did not (or could not) start this project until I found a good soul that promised to help me - I'm really grateful for that. And whoever will participate in this project should be so, too.

VCXOs can synchronize only to frequencies very close to their crystal's frequency, e.g., within +/-100 ppm (+/-0,0001%) or so, this is called the "pull-in range". I aimed that, when the external word clock frequency is outside of this narrow band, the ADC's oscillator runs on its native frequency, and when the frequency is inside of this band, the ADC's oscillator shall be locked to this frequency.

I also aimed that the ADC could easily be extended by the new module with just a simple connection. Once I had an idea how to do it (and the support for the VCXOs), I had to spend most of my time not with design itself, but to fit the necessary circuitry into an affordable CPLD. Only few readers may know how helpless you are when everything but one connection, one output or even one pin-assignment fits into the CPLD and the next bigger one is not only twice as complex but has also twice the physical size and is twice as expensive...

| Last update: February, 15st, 2009 | Questions? Suggestions? Email Me! | Uwe Beis |